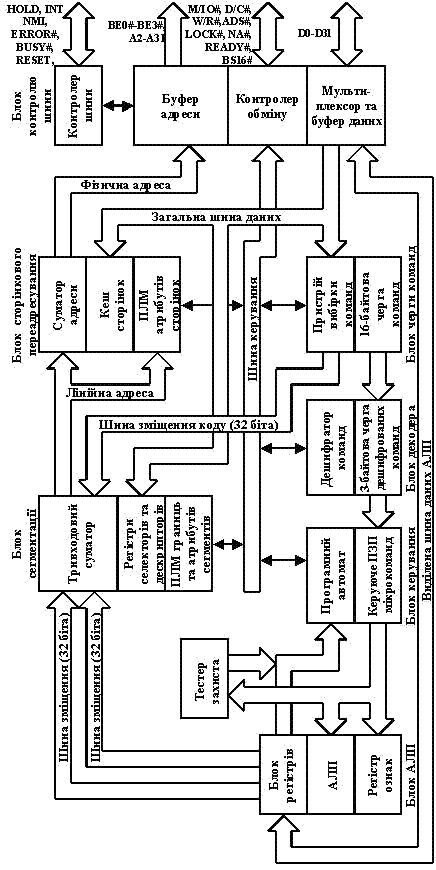

Структура мікропроцесора i386

Структурна схема МП і386 - складається із пристрою обробки (нижня частина схеми), пристрою формування адреси пам’яті (верхня частина схеми) та пристрою узгодження з шиною (права частина схеми).

Пристрій обробки складається із блока АЛП, блока керування, блока декодера, блока черги команд. Блок черги команд складається із пристрою вибірки та 16-байтової черги команд. Пристрій вибірки зчитує команди з пам'яті та розміщає їх у 16-байтовій черзі команд, одночасно пристрій виконує контроль меж сегмента кода. Коди з черги команд надходять у блок декодера де за допомогою дешифратора команд відбувається перетворення коду у дешифрований код інструкції. Дешифровані коди накопичуються у 3-байтовій черзі. По мірі необхідності вони подаються на блок керування. Блок керування складається із керуючого ПЗП мікрокоманд та програмного автомата. На основі дешифрованого коду команди та керуючого ПЗП мікрокоманд програмний автомат формує сигнали керування блоками МП, у тому числі блоком АЛП.

Блок арифметико-логічного пристрою містить вісім 32-бітних регістрів загального призначення об’єднаних у блок регістрів. Вони є взаємозамінними та використовуються у формуванні адреси у різних способах адресації, а також для збереження даних. Частини деяких регістрів МП можуть також використовуватись у програмі для збереження 8- чи 16-бітних чисел. Також у блок АЛП входить арифметико-логічний пристрій (АЛП), що виконує усі арифметичні та логічні операції та регістр ознак, котрий зберігає ознаки результату останньої арифметичної та логічної операції. З вищеназваними блоками зв’язаний блок тестування захисту, що перевіряє коректність адреси результатів та операндів.

Пристрій адресації пам’яті складається із блока сегментації та блока сторінкового переадресування. Блок сегментації, в свою чергу, складається із багатовходового суматора, призначеного для формування адреси, блока селекторних та дескрипторних регістрів та програмованої логічної матриці границь та атрибутів. Блок сторінкого переадресування складається із суматора адреси, кеша сторінок та програмованої логічної матриці контролю.

Блок інтерфейсу шини складається із контролера шини, котрий розподіляє по пріоритетам запити, що надходять на нього, буфера адреси, контролера обміну та мультиплексора-буфера даних. Мультиплексор-буфер даних з’єднаний виділеною шиною з блоком арифметико-логічного пристрою.

Згадані вище блоки мікропроцесора і386 працюють відносно автономно і паралельно. Усі внутрішні шини, що з'єднують ці блоки, мають розрядність 32 біти. Конвеєрна організація функціональних блоків у і386 допускає часове накладання виконання різних стадій команди і дозволяє одночасно виконувати деякі операції. Крім конвеєрного виконання усіх команд, у і386 деякі важливі операції виконуються спеціальними апаратними вузлами. Наприклад арифметико-логічний пристрій (АЛП) виконує множення 32-розрядних чисел за 9–41 такт синхронізації, залежно від кількості значущих цифр. Він може розділити 32-бітні операнди за 38 тактів (у випадку чисел без знаків) чи за 43 такти (у випадку чисел зі знаками).

Пристрій формування адреси також має конвеєрну структуру, з можливістю відключення непотрібних блоків. Операційна система, що керує роботою МП, дозволяє системі реального часу обходити сторінкову переадресацію, або відключити сегментацію пам'яті. Завдяки конвеєрній організації МП має високу швидкодію, у внаслідок чого його продуктивність зазвичай обмежується часом доступу до пам'яті.

Процесор був спроектований так, щоб з максимальною ефективністю використовувати як найбільш швидкодіючі статичні ОЗП, так і недорогі динамічні. Для звертання до швидкої пам'яті, і80386 може виконувати двотактний магістральний цикл. Звертання до повільної пам'яті та пристроїв вводу-виводу може використовувати конвеєрне формування адреси.

Унаслідок внутрішнього конвеєрного формування адреси при виконанні команди і80386, як правило, обчислює адреси й визначає наступний магістральний цикл під час поточного циклу обміну даними. Вузол конвеєрного формування адреси передає цю випереджувальну інформацію у підсистему пам'яті, дозволяючи, тим самим, одному банку пам'яті підготуватись до наступного цикл, у той час як інший банк виконує поточний магістральний цикл.