Формування фізичної адреси МП і386 в захищеному режимі

У захищеному режимі роботи МП і386 використовують три типи адресації:

- логічні адреса – котра складається із сегмента та зміщення. Її використовують аналогічно до логічної адреси МП і80286;

- лінійна адреса – 32-розрідна адреса, котра формується на основі сегмента та зміщення у захищеному режимі роботи. Адреса використовується блоком сторінкової переадресації;

- фізична адреса – адреса, котра формується на основі лінійної блоком сторінкової переадресації та видається на лінії шини адреси.

Захищений режим роботи МП є основним режимом роботи МП. У цьому режимі процесор дозволяє адресувати до 4 Гбайт фізичної пам’яті. Для адресації пам'яті використовують чотири моделі розбиття адресного простору МП:

- лінійну;

- сегментну;

- сторінкову;

- сторінково-сегментну;

У лінійній (плоскій) моделі логічний адресний простір складається з масиву байтів, що не має визначеної структури. Трансляції адрес в цьому випадку не потрібні, оскільки логічна адреса еквівалентна лінійній і фізичній адресі.

У сегментній моделі логічний адресний простір складається із сегментів, кожен з яких містить змінне число байтів. Логічна адреса складається з номера сегмента і зміщення всередині сегмента.

У сторінковій моделі логічний адресний простір складається з набору сторінок, кожна з яких містить фіксовану кількість байтів. Логічна адреса складається з номера сторінки і зміщення усередині сторінки.

У сторінково-сегментній моделі логічний адресний простір складається із сегментів, які, у свою чергу, складаються зі сторінок. Логічна адреса складається з номера сегмента і зміщення усередині сегмента.

У МП і386 можливе використання усіх чотирьох моделей представлення адресного простору.

Сегменти

Сегмент це виділена область адресного простору певної довжини. Сегменти є логічними блоками, які добре пристосовані під програмні структури, що мають змінну довжину. Маючи для сегментів відповідні архітектурні рішення, і386 підвищує продуктивність систем, у яких механізм структурування побудований на сегментах. Сегмент у захищеному режимі МП і386 може мати будь-який розмір від 1 байта до 4 Гбайтів.

Логічний адресний простір задачі складається з одного чи декількох сегментів. Команди і386 посилаються на операнд у пам'яті за допомогою логічної адреси сегмента, що складається із номера сегмента та зміщення у сегменті. У захищеному режимі роботи номер сегмента, називають селектором.

У захищеному режимі роботи вміст сегментного регістра призначений для пошуку базової адреси у спеціальній таблиці базових адрес, що розміщена у пам'яті. Таку таблицю називають дескрипторною, її рядок складається з 64 бітів і носить назву дескриптора. Для кожного сегмента операційна система підтримує заданий дескриптор, що містить опис сегмента. Опис сегмента містить 32-бітну базову адресу сегмента у лінійному адресному просторі, довжину сегмента, а також інформацію про захист, що запобігає неправильному використанню. Додавання зміщення до базової адреси дає лінійну адресу.

У МП і386 трансляція логічної адреси в лінійну оптимізована за допомогою неявної вказівки на селектори і збереження дескрипторів у схованих регістрах МП.

Дескриптори

Дескриптори призначені збереження інформації про сегменти даних, коду та сегменти службового призначення. Дескриптори сегментів коду, даних та деяких службових сегментів (дескриптори шлюзів та задач) поміщають у дескрипторну таблицю.

У дескрипторі задається рівень привілеїв, що може отримати програма при доступі до сегменту. Крім того у дескрипторі задається тип сегмента, його доступність, а також властивості сегмента. Наявність у дескрипторах сегментів прав доступу забезпечує захист від запису у сегменти коду, заборону виконання сегменту даних, контроль за переповненням сегментів стеку, тощо.

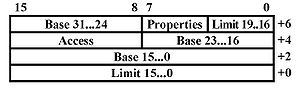

Усі дескриптори можна розділити на дескриптори даних, дескриптори коду та службові дескриптори. Незалежно від призначення дескриптори мають формат зображений на рис.1.

Формування лінійної адреси

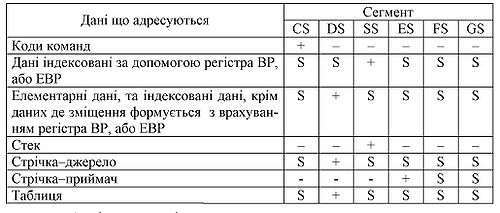

В будь-який момент часу програма може звертатись до одного із 6 сегментів, що відповідають одному з 6 сегментних регістрів. Кожний тип даних, що використовує МП має свій сегментний регістр, якій визначає селектор цих даних. Можливість використання сегментних регістрів з різними типами даних указана у таблиці 1.

У таблиці використані позначення:

+ - сегмент по замовчуванню;

S - сегмент, може використовуватись при наявності спеціальної однобайтової команди (префіксу перекриття сегменту);

- - сегмент неможливо використовувати.

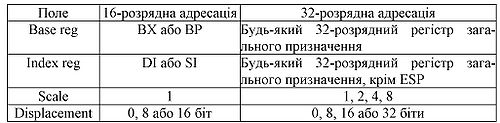

Формування зміщення залежить від режиму адресації, типу команда та типу передачі по шині (вибірка команди, вибірка даних і т.п.). При зчитуванні коду команди зміщення береться з регістра IP (EIP). При роботі зі стеком зміщення береться із регістра SP (ESP). При роботі з "простими" даними формування зміщення здійснюється в залежності від типу команди, що виконується. У МП і386 зняті обмеження на використання регістрів у формуванні зміщення у 32 бітному режимі адресації. Загалом ефективне зміщення Offset в команді вираховується за формулою:

Offset = (Base reg)+(Index reg)*(Scale)+(Displacement),

У формулі використані такі позначення полів:

- Base reg – базовий регістр;

- Index reg – індексний регістр;

- Scale – масштаб;

- Displacement – зміщення у команді.

Залежно від типу адресації даних можливі значення полів змінюються. Можливі значення полів наведені у таблиці 2.

При табличній адресації адреса формується шляхом сумування вмісту регістра AL з регістром BX. Адресація використовується при виконанні команди перекодування по таблиці XLAT.

У випадку використання строкових команд, що використовують строку як джерело даних у якості зміщення обов’язково використовується уміст регістра SI (ESI). Якщо ж команди використовують строку як приймач даних, у якості зміщення використовується уміст регістра DI (EDI).

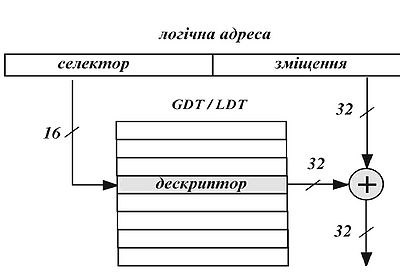

Принцип трансляції логічної адреси у фізичну у мікропроцесорі і386 проілюстрований на рис.2. Уміст селектора використовується для пошуку у локальній чи глобальній дескрипторній таблиці запису (дескриптора), що визначає властивості сегмента та його базову адресу. Базова адреса додається до зміщення у результаті отримується лінійна адреса. Одночасно з формуванням адреси перевіряється доступність сегмента та права доступу до нього.

Формування фізичної адреси

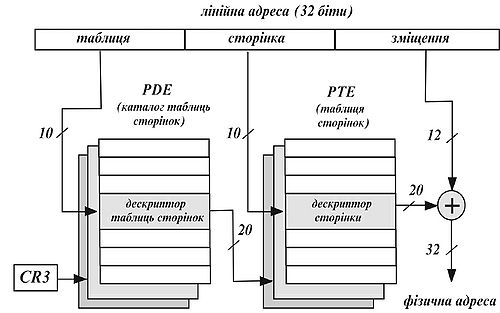

Фізична адреса на основі логічної формується за схемою зображеною на рис. 3.

10 старших розрядів лінійної адреси адресують один зі каталогів таблиць PDE, розташування яких у пам'яті визначається вмістом 32-розрядного системного регістра CR3. 20 старших його розрядів містять базову адресу каталогу таблиць сторінок, а 12 молодших не визначені. Використовуючи старших 10 розрядів лінійної адреси МП здійснює пошук елемента у каталозі таблиць сторінок, який задає базову адресу таблиці сторінок та перевіряє права доступу.

Настуні 10 розрядів лінійної адреси визначають елемент таблиці сторінок. Таблиця сторінок містить 1024 дескриптори, які визначають фізичну адресу початку сторінки пам'яті розміром 4 кбайти. Молодші 12 розрядів визначають зміщення у середині сторінки. Разом з 20 розрядами елемента таблиці сторінок вони формують фізичну адресу комірки пам’яті.

Механізм трансляції сторінок використовується мікропроцесором, якщо старший біт системного регістра CR0 (PG) встановлено в 1. Якщо ж біт рівний "0", то фізична адреса рівна лінійній, а регістр CR3, каталог таблиць сторінок, та таблиці сторінок у формуванні фізичної адреси участі не приймають.

Операційна система, що працює на МП і386 може використовувати розподіл адресного простору за допомогою сегментів та сторінок. Оскільки сегменти можуть перекривати весь адресний простір МП, операційна система може дати задачі лінійний адресний простір без сторінок, або лінійний адресний простір зі сторінок, або адресний простір із сегментів, або адресний простір із сегментів з поділом сегментів на сторінки. Багатоступінчаста трансляція адреси в і386 виконується швидко, типовий час обчислення зміщення і трансляції логічної адреси у фізичну – 1,5 такти.

Для того, щоб зменшити час на пошук адреси у сторінкових таблицях, і386 розміщає довідкову інформацію про 32 останні сторінки, що ним використовувалися, у спеціальний кеш у середині МП. Цю пам'ять називають буфером трансляції сторінок (TLB). Тільки у випадку, якщо мікропроцесор не знаходить інформації про сторінку в TLB, то він звертається до сторінкових таблиць, які розміщуються у пам'яті. Як правило, 98-99% звертань потрапляють у TLB, не вимагаючи звертань до основної пам'яті для трансляції. Коли необхідної інформації у TLB не має, мікропроцесор замінює один з елементів TLB новим елементом, який буде використовуватися надалі.