Відмінності між версіями «Реальний режим роботи»

Lisil (обговорення • внесок) (Створена сторінка: '''Реальний режим роботи''' Мікропроцесора Intel 80286 призначений для з…) |

(Cleaning up links to essaywritingservices.org) |

||

| (Не показано 2 проміжні версії 2 користувачів) | |||

| Рядок 23: | Рядок 23: | ||

*вільний доступ для будь-яких програм, до будь-яких областей даних, що становить потенційну небезпеку для цілісності операційної системи. | *вільний доступ для будь-яких програм, до будь-яких областей даних, що становить потенційну небезпеку для цілісності операційної системи. | ||

| − | Цих недоліків повністю позбавлена схема адресації пам'яті, яка використана у [[Захищений режим роботи | + | Цих недоліків повністю позбавлена схема адресації пам'яті, яка використана у [[Захищений режим роботи|захищеному]] режимі. |

== Зовнішні посилання == | == Зовнішні посилання == | ||

[http://dl.tntu.edu.ua/95/content/14015/ Офіційний сайт ТНТУ] | [http://dl.tntu.edu.ua/95/content/14015/ Офіційний сайт ТНТУ] | ||

Поточна версія на 09:50, 10 березня 2012

Реальний режим роботи Мікропроцесора Intel 80286 призначений для забезпечення найбільшої сумісності з МП і8086. Адресація пам'яті у реальному режимі роботи здійснюється аналогічно до і8086, ніякого захисту програм та даних немає.

Опис роботи

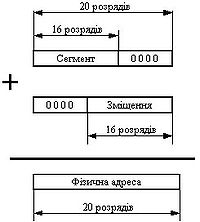

Для адресації пам'яті МП використовує логічні та фізичні адреси. Логічна адреса є 32-бітною незалежно від режиму роботи МП. Вона містить 16-розрядний сегмент та 16-розрядне зміщення. Логічну адресі звичайно записують у формі: сегмент:зміщення. У реальному режимі мікропроцесор звертається до пам'яті, генеруючи 20‑розрядні (точніше, "майже 20-розрядні") фізичні адреси. Формування фізичної адреси здійснюється по правилу зображеному на рис. 8: сегментна частина зсувається на 4 розряди вліво та додається до зміщення. Отже адреси початку сегментів завжди починаються з числа, кратного 16, а кожен сегмент пам'яті має розмір 64 кбайти. Легко довести, що одній фізичній адресі відповідає 16 384 різних логічних адрес. Наприклад: фізичній адресі 00400h (0000 0000 0100 0000 0000b) відповідають логічні адреси 0040:0000 та 0000:0400.

Хоча адресація пам'яті в реальному режимі роботи здійснюється по алгоритму використаному у процесорі і8086, але розробники МП лишили можливість адресувати дані за межами першого мегабайта. Адреса 0F0000:0FFFF відповідає максимально можливій фізичній адресі 0FFFFFh. Але, використовуючи 16-розрядні регістри процесора, є можливість задати і більші значення логічної адреси, наприклад, 0FFFFh:0010h. У даному МП при використанні указаної логічної адреси відбудеться звертання по фізичній адресі 100000h, котра знаходиться за межами першого мегабайта (у МП і8086 було б звертання по адресі 00000h). Тобто у реальному режимі з'являється ще один додатковий сегмент пам'яті, що лежить вище межі першого мегабайта. Цей сегмент називається областю верхньої пам'яті (High Memory Area). Йому відповідає діапазон логічних адрес від 0FFFFh:0010h до 0FFFFh:0FFFFh. Розмір області складає 64 кбайта без 16 байт.

Для досягнення повної сумісності з МП і8086 на системній платі є логічний елемент, що може примусово обнулити лінію A20, проте можливість отримання додаткової пам'яті звичайно переважує можливість звертання до початкових адрес МП і8086 дуже нестандартним чином і таким блокуванням не користуються. Існує також можливість завантаження у сховані регістри МП базової адреси, що знаходиться за межами першого мегабайта по відлагоджувальній команді LOADALL, котра завантажує абсолютно усі регістри МП даними з структури розміщеної по адресам 80:0h-80:66h.

У реальному режимі роботи будь-яка програма може встановити довільні значення в сегментні регістри і адресувати будь-яку ділянку пам'яті. Зокрема, будь-яка програма може навмисно чи через помилку зруйнувати області даних, що належать операційній системі.

У реальному режимі передавання керування виконується за допомогою команд JMP, CALL, INT, RET, IRET, а також при виникненні переривань. При внутрішньосегментньому передаванні керування у регістр IP заноситься нове значення, а регістр CS не модифікується. Міжсегментне передавання і одночасно змінює регістри CS і IP, а також у деяких випадках і регістр ознак F (переривання і команди RET, IRET).

Внутрішньосегментне передавання керування виконується командами JMP, CALL, RET, а міжсегментна передача керування – командами JMP, CALL, INT, RET, IRET і у випадку виникнення переривань.

У реальному режимі будь-якій програмі дозволяється робити перехід на будь-яку адресу, або викликати будь-які підпрограми та переривання. Є можливість здійснити перехід на команди початкової ініціалізації системи або спробувати виконати дані. Єдина умова для успішного виклику підпрограми – знання адреси підпрограми (сегмента і зміщення) і формату переданих даних.

Недоліки

Отже два основні недоліки реального режиму:

- обмежений адресний простір;

- вільний доступ для будь-яких програм, до будь-яких областей даних, що становить потенційну небезпеку для цілісності операційної системи.

Цих недоліків повністю позбавлена схема адресації пам'яті, яка використана у захищеному режимі.